|

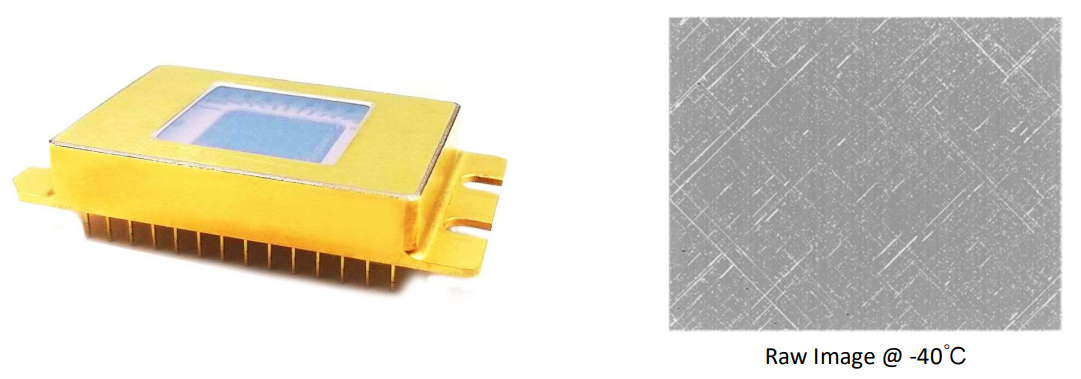

Product Features:

- 320X256 Array Format

- 28-pin Metal DIP Package

- Embedded Thermoelectric Cooler

- Built-in Temperature Sensor

- 1.2 μm – 2.2 μm Spectral Range

- Typical Pixel Operability > 98%

- Quantum Efficiency > 65%

- Snapshot ITR / IWR and IMRO Readout Modes

- 1, 2 or 4 Outputs with up to 10 MHz Pixel Rate

- windowing Capability

Applications:

- Near-Infrared Imaging

- Imaging Spectroscopy

- Medical Science and Biology

SPECIFICATIONS (ITS = -40ºC)(Readings from Integrated Temperature Sensor (ITS)):

Parameters

|

Symbol

|

Test conditions

|

Min

|

Typ |

Max

|

Unit |

Sensor Technology

|

|

|

Planar InGaAs PIN

|

|

Actual Pixel Array

|

|

|

320x256

|

|

Effective Pixel Array

|

|

|

318x254

|

|

Pixel Pitch

|

|

|

30

|

µm

|

Spectral Response Range

|

λ

|

|

1200

|

|

2200

|

nm

|

Dark Current(*)(**)

|

|

Pixel bias @ 0V

|

|

|

10

|

pA

|

Quantum Efficiency*Fill Factor(*)

|

QEFF

|

λ = 1.7µm

|

65 |

|

|

%

|

Response Nonuniformity(*)

|

|

At 50% Full Well

|

|

|

10

|

%

|

Response Nonlinearity(*)

|

|

15%-85% Well Occupation Range

|

|

|

10

|

%

|

Charge Capacity

(ROIC Specifications)

|

|

@High Gain, 13.3µV/e-

|

|

0.17

|

|

Me-

|

@Low Gain, 0.7µV/e-

|

|

3.5

|

|

Readout Noise

|

|

ROIC Specifications

|

|

|

70 |

e-RMS

|

Output Swing

|

|

|

|

2.7

|

|

V

|

Minimum Integration Period

|

|

Assuming 5MHz Master Clock

|

|

5.5

|

|

µs

|

Pixel Operability(*)

|

|

Percentage of Pixels with QEFF Deviation ± 45%*(QEFF Mean) |

98

|

|

|

%

|

Image Size

|

|

|

9.6 x 7.68

|

mm

|

Package Type

|

|

|

28-pin Metal DIP Package

|

|

Package Size L X W X T

|

|

|

50.0 X 25.4 X 11.67

|

mm

|

Weight

|

|

|

24.0

|

g

|

Note (*): Pixel Operability is defined within the center 318x254 regions.

Note (**): Low Gain, Tint = 4ms –0.01ms.

Absolute Maximum Ratings:

| |

Parameters

|

Min

|

Typ |

Max

|

Unit |

| |

Operating Temperature

|

-40

|

|

71

|

°C

|

| |

Storage Temperature

|

-40

|

|

71

|

°C

|

| |

Power Consumption (*)

|

|

|

175

|

mW

|

| |

TEC Bias

|

|

|

4.8

|

V

|

| |

TEC Current

|

|

|

1.8

|

A

|

Note (*): Without powering on the thermoelectric cooler.

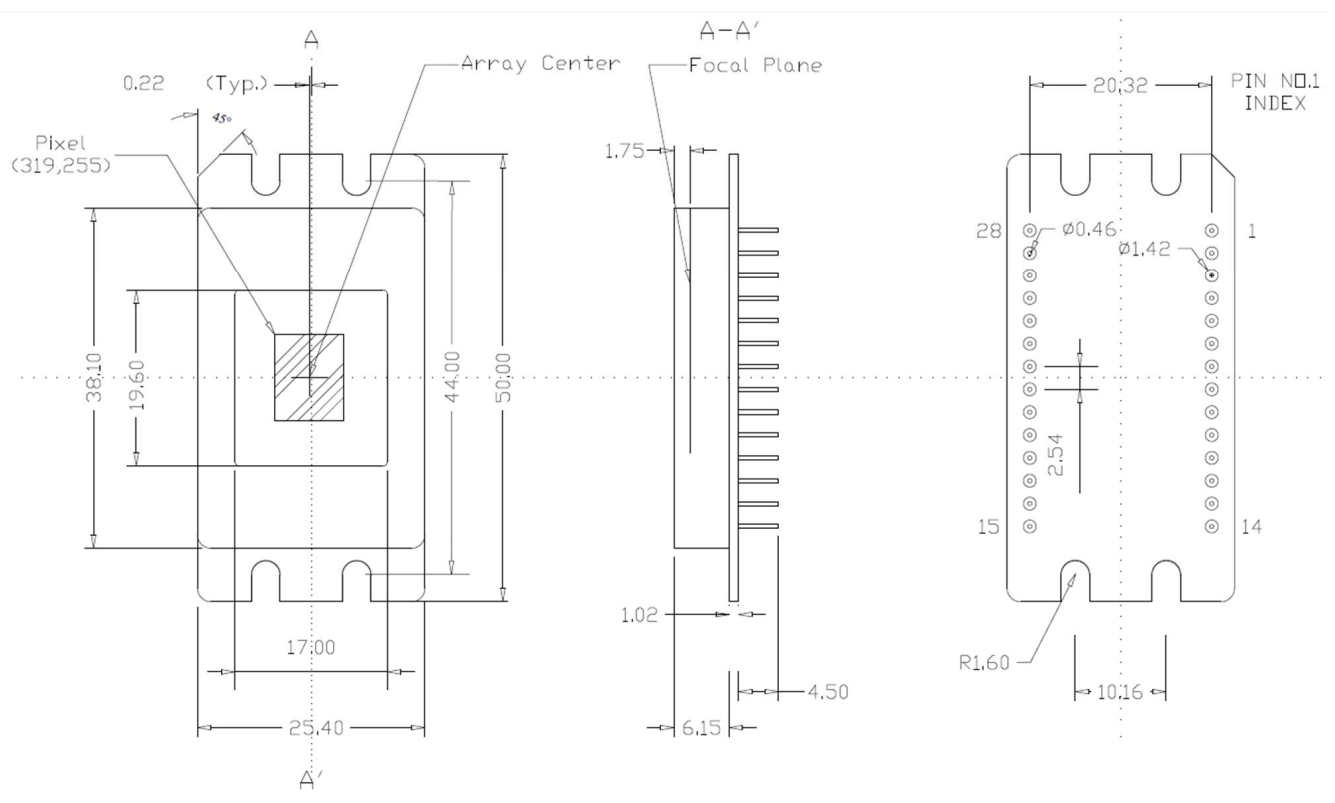

Package Dimensions (mm):

| |

01

|

VPOS

|

08

|

DATA |

15

|

VNEGOUT

|

22

|

VOS |

| |

02

|

VDETCOM

|

09

|

FSYNC |

16

|

OUTA

|

23

|

VBLM |

| |

03

|

TEC+

|

10

|

LSYNC |

17

|

OUTB

|

24

|

VOUTREF |

| |

04

|

VPOS_CORE

|

11

|

CLK |

18

|

OUTC

|

25

|

VCAS |

| |

05

|

TEMP

|

12

|

VPD |

19

|

OUTD

|

26

|

TEC- |

| |

06

|

BWL

|

13

|

VND |

20

|

OUTR

|

27

|

IMSTR ADJ |

| |

07

|

GAIN

|

14

|

CASE GROUND |

21

|

VPOSOUT

|

28

|

VNEG |

Bias Input :

| |

Pin #

|

Bias

|

Voltage |

Current

|

Remark |

| |

12

|

VPD

|

5.5V |

<1mA

|

Logic positive supply

|

| |

13

|

VND

|

0V |

<1mA

|

Logic negative supply

|

| |

21

|

VPOSOUT

|

5.5V |

<25mA

|

Output stage analog supply

|

| |

15

|

VNEGOUT

|

0V |

<25mA

|

Output stage analog ground

|

| |

1

|

VPOS

|

5.5V |

<5mA

|

Positive analog supply

|

| |

28

|

VNEG

|

0V |

<15mA

|

Negative analog supply and

substrate

|

| |

4

|

VPOS_CORE

|

5.5V |

<15mA

|

CTIA amplifier positive supply

|

| |

2

|

VDETCOM

|

4.5V~5.0V |

<5mA

|

Detector common voltage

Detector bias = VDETCOM-4.5

|

Digital Pattern Input :

| |

Pin #

|

Clocks

|

Levels |

Rise/Fall

|

Remark |

| |

11

|

CLK

|

0V~5.5V |

<10ns

|

Master clock Max. Freq.=5MHz

|

| |

9

|

FSYNC

|

0V~5.5V |

<10ns

|

Frame sync - controls frame start and

integration time

|

| |

10

|

LSYNC

|

0V~5.5V |

<10ns

|

Line sync - controls line readout

timing

|

| |

8

|

DATA

|

0V~5.5V |

<10ns

|

Data code input - programs device

function registers in Control Mode

Left open in Default Mode

|

| |

Clocks

|

Synchronization |

| |

FSYNC

|

Rising and falling when CLK is rising

|

| |

LSYNC

|

Rising and falling when CLK is falling

|

| |

DATA

|

Rising and falling when CLK is rising

|

Video Output :

| |

Pin #

|

Outputs

|

Levels |

Settle

|

Remark |

| |

16

|

OUTA

|

1.3V to 4.2V |

<50ns to

0.1%

|

Output A used in single output

mode

|

| |

17

|

OUTB

|

1.3V to 4.2V |

<50ns to

0.1%

|

Output A and B used in two

output mode

|

| |

18

|

OUTC

|

1.3V to 4.2V |

<50ns to

0.1%

|

Output A, B, C, and D used in

four output mode

|

| |

19

|

OUTD

|

1.3V to 4.2V |

<50ns to

0.1%

|

Output A, B, C, and D used in

four output mode

|

| |

20

|

OUTR

|

3V |

|

Reference for common mode

output

|

Gain & Bandwidth Selection in Default Mode :

| |

Pin #

|

Functions

|

Low |

High

|

Remark |

| |

7

|

GAIN

|

0V / C=10fF |

5.5V / C=210fF

|

Selects unit cell integration

capacitor

Left open in Control Mode |

| |

6

|

BWL

|

0V / Low BW |

5.5V / High BW

|

Selects bandwidth limiting capacitor

in unit cell

Left open in Control Mode |

Advanced Function :

| |

Pin #

|

Functions

|

Voltages |

Remark |

| |

25

|

VCAS(*)

|

3.75V |

CTIA amplifier cascode FET biase |

| |

24

|

VOUTREF(*)

|

3V |

Output reference level during blanking period |

| |

23

|

VBLM(*)

|

2V |

Detector bloom control |

| |

27

|

IMSTR_ADJ(**)

|

0V~5.5V |

Adjusts analog master bias current |

| |

22

|

VOS

|

0V~5.5V |

Variable Offset/Skimming Control Voltage |

| |

5

|

TEMP

|

0V~5.5V |

On chip temperature monitor

0.74V at 300K Slope=-14.8mV/10K in 50-300K |

Note (*): Internally generated after bias input, but can be overridden.

Note (**): Also addressable through control register (DATA).

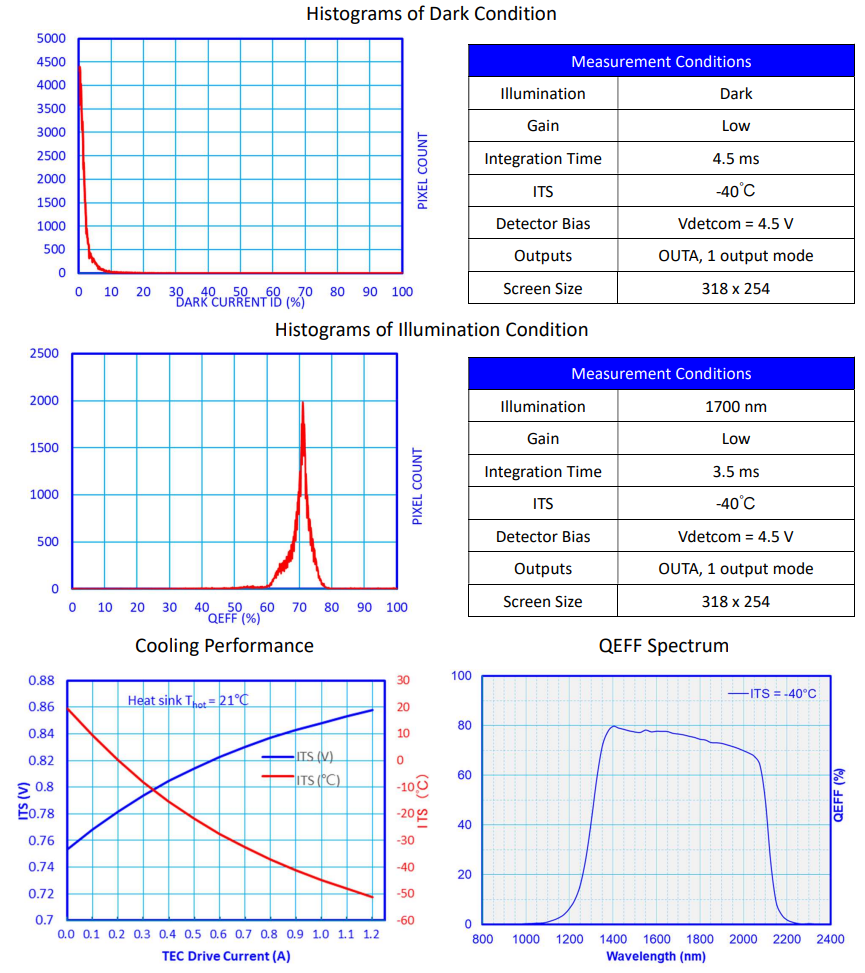

EXAMPLE CURVES :

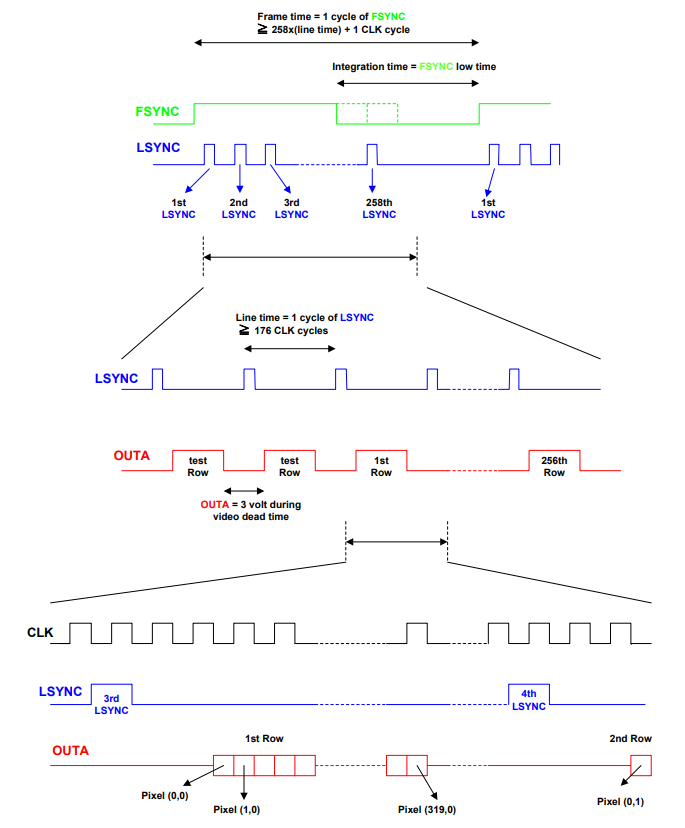

TIMING CHART FOR DEFAULT MODE OPERATION :

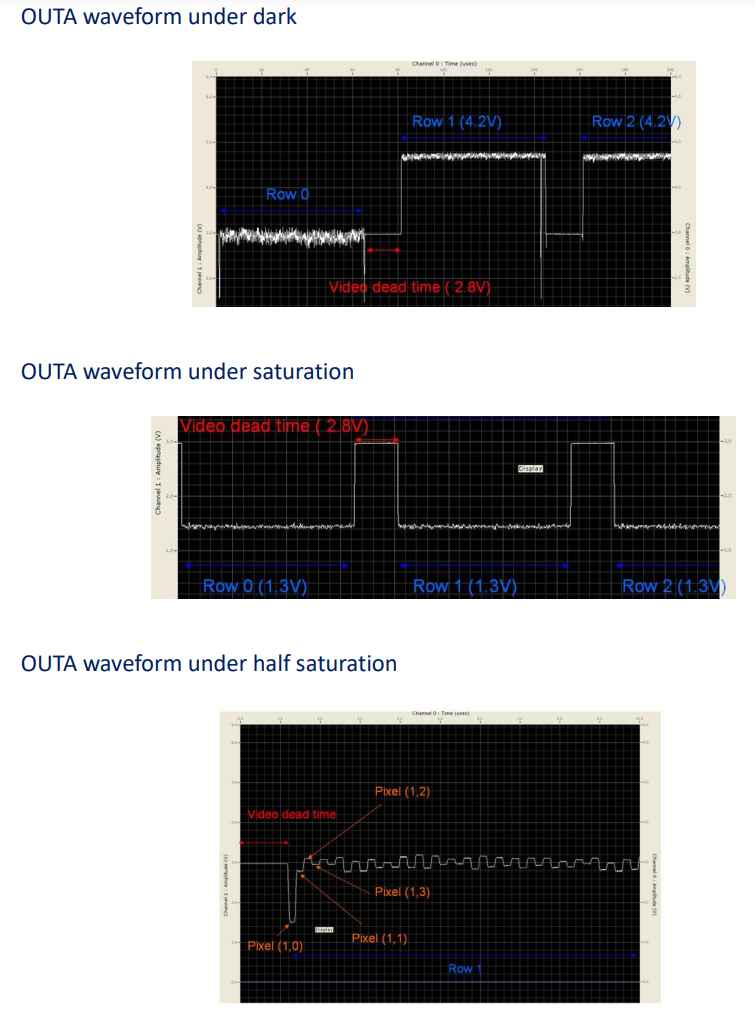

OUTA Waveform :

|